Контрактний виробник напівпровідникових виробів TSMC, що контролює більше половини ринку відповідних послуг, на щорічному заході Technology Symposium розкрив подробиці не тільки про 3-нм технології, але і про подальші розробки.

Перш за все, компанія визнала за потрібне в черговий раз повідомити, що затримок з освоєнням 3-нм технології не очікується. Дослідне виробництво 3-нм чіпів буде запущено в наступному році, а до стадії масового виробництва компанія добереться в другій половині 2022 року. Перед цим 5-нм техпроцес у своєму розвитку теж пройде кілька стадій.

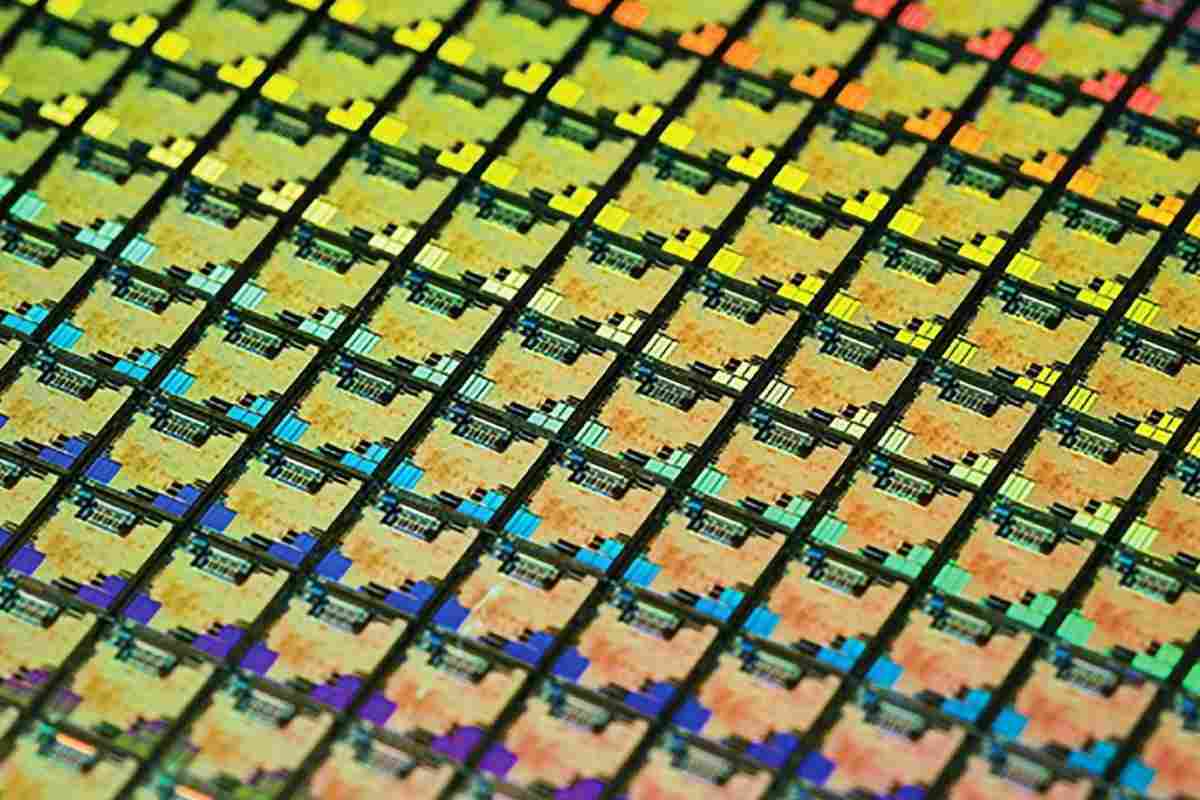

Зараз вже випускаються 5-нм продукти першого покоління. Вони забезпечують приріст швидкодії транзисторів на 15% порівняно з 7-нм виробами або дозволяють знизити енергоспоживання на 30% при незмінній продуктивності. Щільність розміщення транзисторів при цьому зросла в 1,8 рази порівняно з 7-нм техпроцесом.

Друге покоління 5-нм техпроцесу з умовним позначенням N5P дістанеться до стадії масового виробництва наступного року. Воно підніме швидкодію транзисторів на 5%, або дозволить на десять відсотків знизити енергоспоживання. Заготовлений у TSMC і так званий 4-нм техпроцес (N4), який стане більш дешевою альтернативою 3-нм. Дослідне виробництво 4-нм продукції стартує в четвертому кварталі наступного року, масове - тільки в 2022 році.

Освоєння 5-нм техпроцесу з точки зору щільності дефектів зараз просувається з випередженням на квартал щодо графіка, притаманного 7-нм технології. Якщо говорити про 3-му техпроцесі у виконанні TSMC, то компанія збирається спиратися на вже перевірені FinFET-структури, на відміну від Samsung, яка експериментує з так званими GAA-транзисторами (gate-all-around, «повністю оточені затворами»).

Техпроцес 3 нм дозволить підняти швидкодію транзисторів на 10-15% відносно 5 нм, або скоротити енергоспоживання на 25-30% при аналогічній продуктивності. Щільність розміщення транзисторів повинна збільшитися в 1,7 рази. Осередки пам'яті SRAM при переході на 3-нм техпроцес збільшать щільність розміщення елементів на 20%, аналогові компоненти можуть обмежитися збільшенням щільності в 1,1 рази.

Еру «після 3 нм» TSMC збирається підкорювати вже за допомогою альтернативних матеріалів, а не тільки кремнію. Вуглецеві нанотрубки і нанопровідники повинні отримати поширення в цій сфері. Розробки на даному напрямку TSMC веде ще з 2019 року, але консерватизм щодо 3-нм техпроцесу дозволяє припустити, що в серійному виробництві компанія буде впроваджувати тільки найбільш перевірені і надійні рішення.